导航

微信

顶部

发布时间:2026-02-06 阅读: 来源:管理员

在实际项目中,很多企业一遇到SMT良率低,第一反应往往是:

- 贴片机不行

- 钢网没开好

- 焊膏有问题

但从大量PCBA量产案例来看,真正“改不动”的问题,往往出在PCB设计阶段。

PCB设计一旦定稿,以下内容就被“锁死”了

- 焊盘尺寸

- 器件间距

- BGA扇出方式

- 电源/地回流路径

- 是否满足DFM/DFT

如果这些基础条件不合理,哪怕SMT设备再先进,也只能“硬贴”,良率自然上不去。

1. 焊盘设计不合理,是SMT缺陷的高发源头

常见问题包括:

- 焊盘过大 → 连锡、桥连

- 焊过小 → 虚焊、立碑

- 非标准封装 → 贴装偏移、漏件

设计建议:

- 焊盘尺寸应优先参考IPC-7351标准封装库

- BGA、QFN、LGA 等器件避免“经验画焊盘”

- 对于细间距器件,焊盘尺寸需结合钢网厚度综合评估

2. 器件布局混乱,SMT再调也救不了

合理的PCB布局,直接决定了SMT贴装的“顺不顺”。

不合理布局常见表现:

- 元件过密,贴片头无法避让

- 同一方向器件角度混乱,降低贴装效率

- 大小件混排,导致回流焊受热不均

优化思路:

- 同类器件尽量统一方向(尤其是IC、电阻、电容)

- 大功率器件、热敏器件与普通器件合理分区

- BGA周边预留足够贴装与检测空间

这一步,PCB设计工程师是否理解SMT工艺限制非常关键。

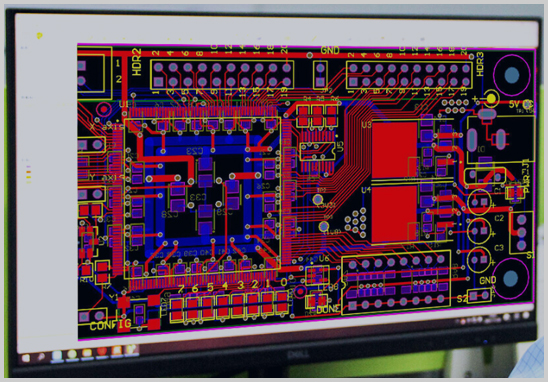

3. BGA / 高密度PCB设计,直接决定贴装成功率

对于 BGA、多层、高密度PCB 来说,SMT良率更依赖前期设计。

设计中常见“隐形雷点”:

- BGA焊盘阻焊定义错误(SMD / NSMD未区分)

- 扇出方式不合理,导致焊点受力异常

- 盲孔、埋孔位置影响焊盘完整性

设计建议:

- 优先采用 NSMD焊盘,提升焊点可靠性

- 合理规划盲孔/埋孔,避免侵占焊盘区域

- 高密度板建议在设计阶段就做 SMT可制造性评估

4. 走线与过孔设计,也会影响焊接质量

很多人忽略:走线方式,也会间接影响SMT良率。

例如:

- 过孔靠近焊盘 → 回流焊时“吸锡”

- 电源/地回流不顺 → 焊点受热不一致

- 高速信号与焊盘连接不对称 → 器件偏移

建议:

- 焊盘附近避免直接打过孔(必要时采用塞孔/树脂填孔)

- 电源、地平面完整,减少局部温差

- 关键焊盘走线尽量保持对称

真正为量产负责的PCB设计,一定不是“只画通”。

DFM(可制造性设计)

- 是否符合SMT贴装、回流焊、AOI检测要求

- 是否考虑钢网、贴片精度、公差叠加

DFT(可测试性设计)

- 测试点是否充足、位置是否合理

- 是否影响ICT / FCT测试覆盖率

很多SMT问题,不是焊不上,而是“测不出来、返修难”,最终拉低整体良率。

从实际项目经验看

PCB设计 + PCBA分离,往往会带来:

- 设计不考虑贴装可行性

- 量产前频繁改板

- SMT试产良率低,反复调工艺

而从PCB设计阶段就引入SMT/PCBA经验,可以提前规避80%以上的问题。

作为专业PCB设计服务公司,宏力捷电子在设计阶段就重点关注SMT良率与量产可行性:

- 多层、高精密、BGA、盲孔/埋孔PCB设计

- 基于IPC标准的规范封装与焊盘设计

- 设计阶段同步DFM/DFT评估

- 从原理图 → PCB设计 → BOM → 采购 → 打样 → PCBA量产一站式服务

对客户来说,好处只有一个:

一次设计,顺利贴装,减少反复改板和返工成本

如果你正在遇到以下问题:

- SMT贴装良率低

- 新产品试产反复修改

- BGA板子“看着没问题,但总是虚焊”

那不妨回到源头看看:

你的PCB设计,真的为SMT量产考虑过吗?

获取报价